Simulation model for routes in public transport systems using parallel computing in IoT environments

Doctoral Thesis

#### PhD(c) Eng. Juan Pablo Ruiz Rosero

Advisor: PhD. Eng. Gustavo Adolfo Ramírez González Co-advisor: PhD. Eng. Rahul Kahanna

Universidad del Cauca Facultad de Ingeniería Electronica y Telecomunicaciones Doctorado en Ingeniería Telemática Departamento de Telemática Línea de Investigación en Aplicaciones sobre Internet Popayán, November 2019

To my wife Carolina and my son Jacobo

# Acknowledgments

I want to give my acknowledgements thanks to my supervisor, PhD. Gustavo Ramirez for his open doors to help me to improve any crazy idea in this project. Thanks to my cosupervisor PhD. Rahul Kahanna for several contributions to the research work. Thanks to Intel Corporation, to the Internet of Things Group, and to Greeshma Pisharody due to their hosting during the research stay. Thanks to the University of Cauca, specially to the Telematics Engineer Group for their financial and administrative support. Finally, thanks to Colciencias, because this work was funded by the Departamento Administrativo de Ciencia, Tecnología e Innovación (647-2014). This work could not be possible without any of the aforementioned persons and institutions, therefore my sincere and heartfelt thanks to them.

# Abstract

#### Background

There are a large number of tools for the simulation of traffic and routes, which take into account the different simulation models (macroscopic, microscopic, and mesoscopic). Unfortunately, these simulation tools are limited when simulating a complete public transport system, which includes all its buses and routes (up to 270 for the London Underground). The processing times for this type of simulation increase in an unmanageable way, since all the relevant variables that are required to simulate consistently and reliably the system behavior must be evaluated. Different studies nationwide have encountered this problem. In these, tools have been generated for the simulation and optimal allocation of routes in mass transport systems such as Transmilenio in Bogotá, Colombia, concluding that current simulation models cannot simulate systems of public transport completely. This problem is because they represent a large-scale NP-hard problem, in which the time required for simulation increases exponentially when a new element is added.

At present, the processing capacity of modern computers is no longer measured based on the clock frequency of their CPUs, since the limit allowed by silicon has been reached (around 4GHz). Today the processing capacity depends more on the number of cores and the amount and speed of RAM. Unfortunately, to the date, there are no enough models for the simulation of the behavior of routes in public transport systems that take advantage of the benefits of parallel processing provided by modern computer systems, such as GPUs, or other parallel processing architectures. Therefore, we found that there is a lack of simulation models that can handle the behavior of all routes of a public transport system efficiently and consistently, taking advantage of parallel computing.

#### Aims

The main aim of this project is the purpose of a new public transport systems' routes simulation model for parallel computing architecture in IoT environments. This aim comprises the following objectives:

- Identify the input and output variables for a routes simulation model in public transport systems, from IoT environments.

- Define a parallel computing architecture that is efficient for the execution of route simulation models in public transport systems.

- Construct a new simulation model for the defined parallel computing architecture, which, through the identified input and output variables, allows the simulation of routes in public transport systems to be carried out efficiently and consistently.

- Validate the consistency of the new simulation model using other simulation models already validated.

- Evaluate the performance of the new simulation model, in contrast to other models executed in different architectures.

## Methods

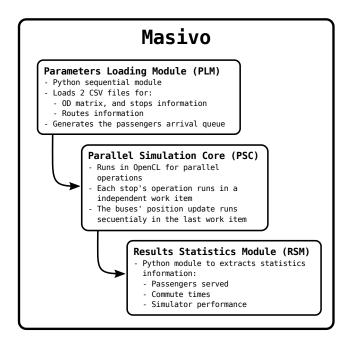

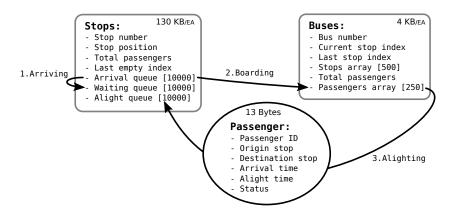

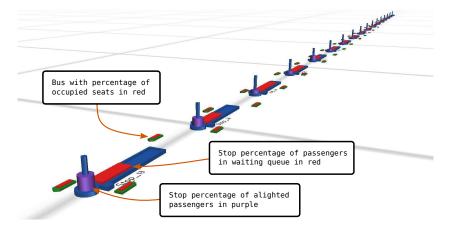

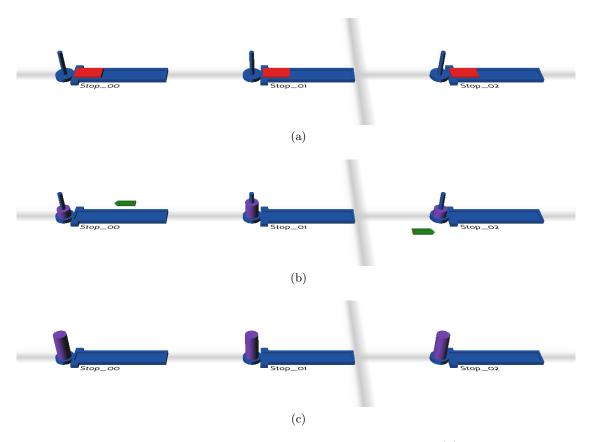

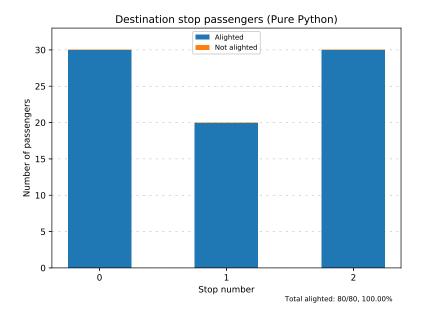

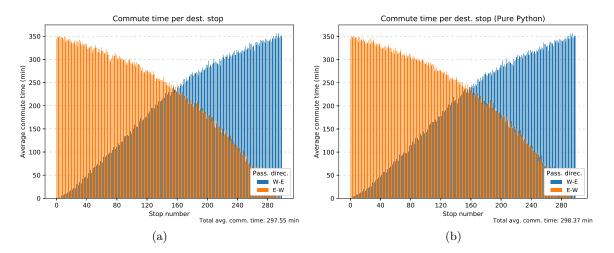

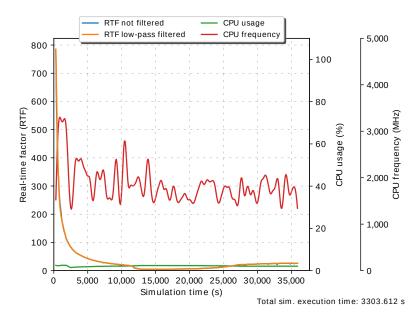

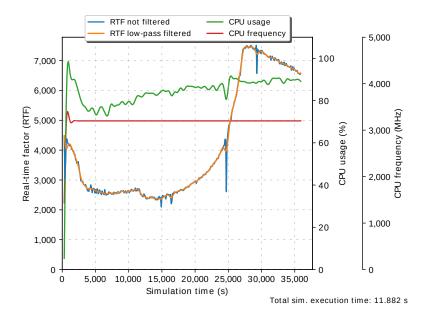

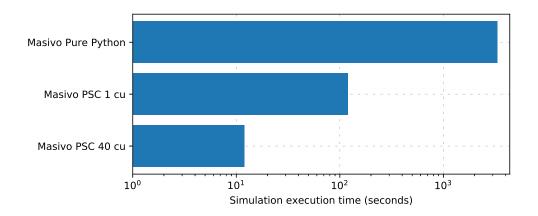

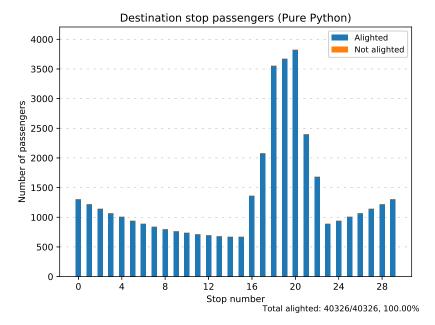

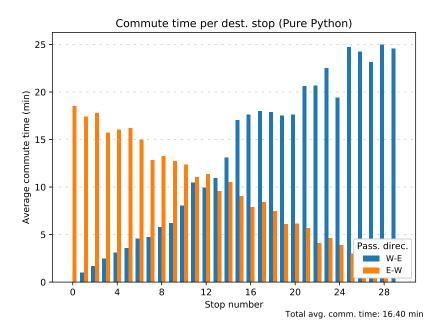

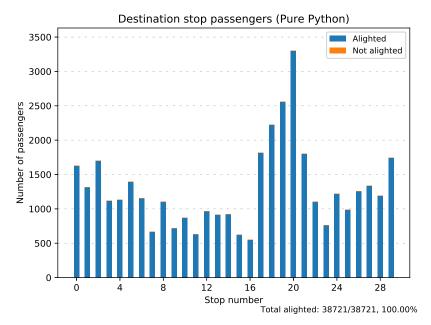

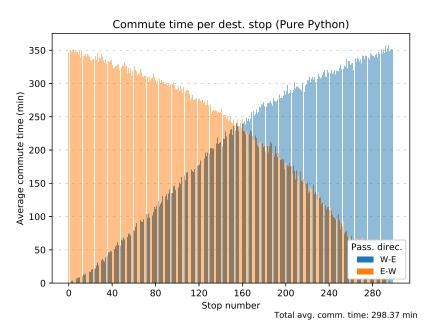

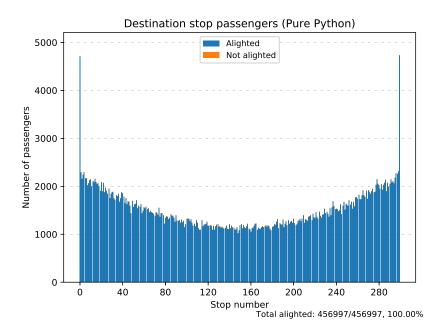

A scientometric tool called ScientoPy was built to support the state of the art analysis. In state of the art, we reviewed the applications for the Internet of Things focusing on Smart Cities and then in Intelligent Transport Systems. Then, we review the applications for the three main parallel processing architectures: GPU, FPGA, and multi-core to find parallel implementations for public transport simulation. Next, a validation public transport simulator was build entirely in Python with dynamic lists to emulate the passengers' queues in the stops and buses. We named this as Pure Python simulator. The behavior of this simulator was validated with the simulation output data consistency and with the graphical real-time 3D output that shows the passengers and buses' movement in the system. Then, we designed and built a parallel simulation model called Masivo PSC (Parallel Simulation Core) then performs concurrently the arrival, boarding, and alighting operations per each stop in a separate work item that runs in OpenCL. Furthermore, we validated the Masivo PSC simulation outputs with the Pure Python simulator outputs for 4 scenarios. Finally, we extracted the simulator performance indicators for the most complicated scenario with 300 stops and near to 500,000 passengers.

### Results

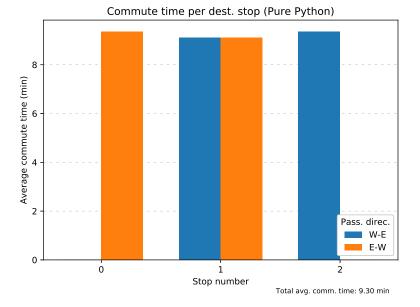

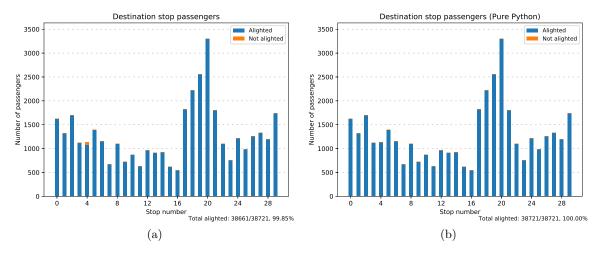

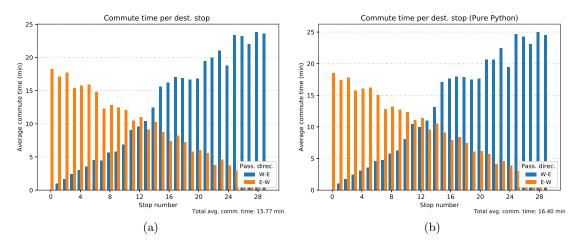

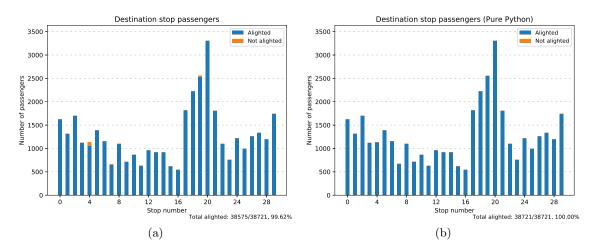

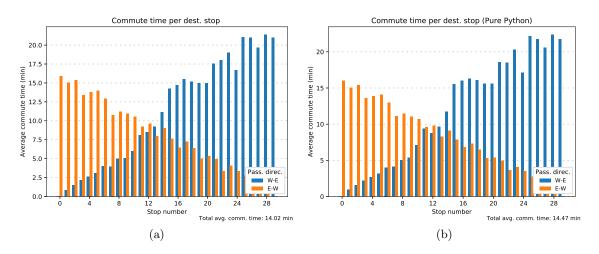

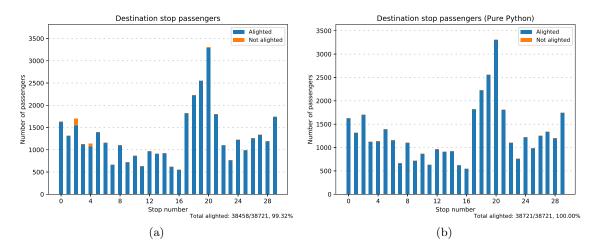

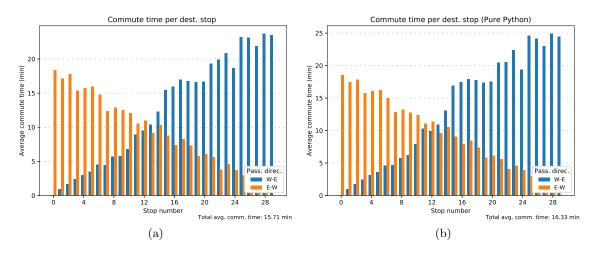

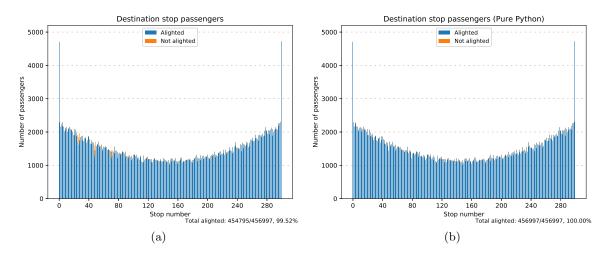

In the validation results, we found that the relative error for the total alighted passengers and the total average commute time is not greater than 0.7 % in all of the 4 tested scenarios. The performance results of Masivo show a speed-up factor of 10.2 compared with the simulator model running with one compute unit, and speed-up factor of 278 times faster than the Pure Python validation simulator. The real-time factor achieved was 3050 times faster than the 10 hours simulated duration.

### Conclusions

A new simulation model for routes in public transport systems using parallel computing in IoT environments, called Masivo PSC was generated. Masivo works with a predefined public transport system conditions, which include the stops total number, stops' capacity, and the OD matrix. This OD matrix and routes information can be updated to this model via CSV files. Masivo gets the simulation results for total alighted passengers and average commute time. Similarly, it shows the performance indicators.

## Keywords:

$simulation,\ parallel,\ multi-core,\ public\ transport,\ OpenCL.$

# Resumen

#### Antecedentes

Hay una gran cantidad de herramientas para la simulación de tráfico y rutas en sistemas de trasnporte público, que tienen en cuenta los diferentes modelos de simulación (macroscópica, microscópica y mesoscópica). Desafortunadamente, estas herramientas de simulación son limitadas cuando se simula un sistema de transporte público completo, que incluye todos sus autobuses y rutas (hasta 270 para el caso del metro de Londres). Los tiempos de procesamiento para este tipo de simulaciónes aumentan de manera inmanejable, ya que todas las variables relevantes que se requieren para simular de manera consistente y confiable el comportamiento del sistema deben ser evaluadas. Diferentes estudios a nivel nacional han encontrado este problema. En estos, se han generado herramientas para la simulación y asignación óptima de rutas en sistemas de transporte masivo como Transmilenio en Bogotá, Colombia, concluyendo que los modelos de simulación actuales no pueden simular completamente los sistemas de transporte público. Este problema se debe a que representan un problema NP-hard a gran escala, en el que el tiempo requerido para la simulación aumenta exponencialmente cuando se agrega un nuevo elemento.

En la actualidad, la capacidad de procesamiento de las computadoras modernas ya no se mide en función de la frecuencia de reloj de sus CPU, ya que se ha alcanzado el límite permitido por el silicio (alrededor de 4 GHz). Desafortunadamente, hasta la fecha, no existen modelos suficientes para la simulación del comportamiento de las rutas en los sistemas de transporte público que aprovechan los beneficios del procesamiento paralelo proporcionado por los sistemas informáticos modernos, como las GPU u otras arquitecturas de procesamiento paralelo. Por lo tanto, descubrimos que faltan modelos de simulación que puedan manejar el comportamiento de todas las rutas de un sistema de transporte público de manera eficiente y consistente, aprovechando la computación paralela.

#### Objetivos

El objetivo principal de este proyecto proponer un nuevo modelo de simulación de rutas en sistemas de transporte público para una arquitectura de computación paralela, en entornos IoT. Este objetivo comprende los siguientes objetivos:

- Identificar las variables de entrada y salida para un modelo de simulación de rutas en sistemas de transporte publico, desde los entornos IoT.

- Definir una arquitectura de computación paralela que sea eficiente para la ejecución de modelos de simulación de rutas en sistemas de transporte público.

- Construir un nuevo modelo de simulación para la arquitectura de computación paralela definida, que mediante las variables de entrada y salida identificadas, permita realizar de manera eficiente y consistente la simulación de rutas en sistemas de transporte público.

- Validar la consistencia del nuevo modelo de simulación mediante otros modelos de simulación ya validados.

- Evaluar el rendimiento del nuevo modelo de simulación, en contraste con otros modelos ejecutados en diferentes arquitecturas.

## Métodos

Se creó una herramienta cienciométrica llamada ScientoPy para soportar el análisis del estado del arte. En este estado del arte, revisamos las aplicaciones para el Internet de las cosas centrándose en las ciudades inteligentes y luego en los sistemas inteligentes de transporte. Luego, revisamos las aplicaciones para las tres arquitecturas principales de procesamiento paralelo: GPU, FPGA y multi-core para encontrar implementaciones para la simulación del transporte público. A continuación, se construyó un simulador de transporte público de validación completamente en Python con listas dinámicas para emular las colas de los pasajeros en las paradas y autobuses. A este simulador lo denominamos Pure Python simulator. El comportamiento de este simulador se validó con la consistencia de los datos de salida de la simulación y con la salida gráfica en 3D en tiempo real que muestra el movimiento de los pasajeros y autobuses en el sistema. Luego, diseñamos y construimos un modelo de simulación paralela llamado Masivo PSC (Parallel Simulation Core) que ejecuta en paralelo las operaciones de llegada, embarque y desembarque por cada parada en un work-item independiente que se ejecuta en OpenCL. Además, validamos los resultados de la simulación de Masivo PSC con los resultados del simulador Pure Python para 4 diferentes escenarios. Finalmente, extrajimos los indicadores de rendimiento del simulador para el escenario más complicado con 300 paradas y cerca de 500,000 pasajeros.

## Resultados

En los resultados de la validación, encontramos que el error relativo para el total de pasajeros desembarcados y el tiempo de viaje promedio total no es mayor que el 0.7 % en los 4 escenarios probados. Los resultados de rendimiento de Masivo muestran un speed up factor de 10.2 comparado con el mismo ejecutado en una sola unidad de cómputo, y un speed up factor de 278 veces más rápido que el simulador de validación Pure Python. El real-time factor alcanzado fue de 3050 veces más rápido que el tiempo total simulado de 10 horas.

## Conclusiones

Se generó un nuevo modelo de simulación para rutas en sistemas de transporte público que usa computación paralela en entornos IoT, llamado Masivo PSC. Masivo trabaja con un sistema de transporte público predefinido, que incluye el número total de paradas, la capacidad de las paradas y la matriz de origen-destino.

### Palabras clave:

$simulación,\ paralelo,\ multi-core,\ transporte\ público,\ OpenCL.$

# Contents

| 1.2 Objectives       3         1.2.1 General Objective       3         1.2.2 Specific Objectives       4         2 State of the art       5         2.1 Methodology based on ScientoPy scientometric analysis       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1        | Intr        | oduction                                              | 1        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------------------------------------------------|----------|

| 1.2.1       General Objective       3         1.2.2       Specific Objectives       4         2       State of the art       5         2.1       Methodology based on ScientoPy scientometric analysis       6         2.1.1       Methodology       7         2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.4       Research Topics       31         2.3.5       Networking       43         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10 |          | 1.1         | Problem statement                                     | 1        |

| 1.2.1       General Objective       3         1.2.2       Specific Objectives       4         2       State of the art       5         2.1       Methodology based on ScientoPy scientometric analysis       6         2.1.1       Methodology       7         2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.1.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11  |          | 1.2         | Objectives                                            | 3        |

| 1.2.2       Specific Objectives       4         2       State of the art       5         2.1       Methodology based on ScientoPy scientometric analysis       6         2.1.1       Methodology       7         2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11     |          |             | -                                                     | 3        |

| 2.1       Methodology based on ScientoPy scientometric analysis       6         2.1.1       Methodology       7         2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60   |          |             |                                                       | 4        |

| 2.1.1       Methodology       7         2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1  | <b>2</b> | Sta         | e of the art                                          | <b>5</b> |

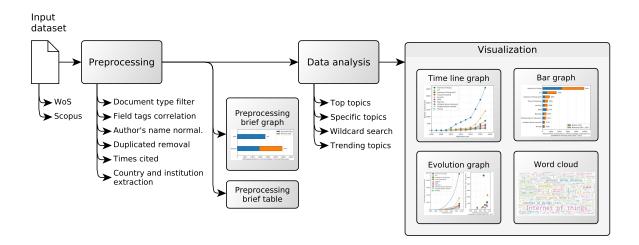

| 2.1.2       User graphic interface (ScientoPyUI)       18         2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       41         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic pr   |          | 2.1         | Methodology based on ScientoPy scientometric analysis | 6        |

| 2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing u   |          |             | 2.1.1 Methodology                                     | 7        |

| 2.1.3       Comparative with other scientometric tools       19         2.2       Internet of things       22         2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing u   |          |             | 2.1.2 User graphic interface (ScientoPyUI)            | 18       |

| 2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       43         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                            |          |             |                                                       | 19       |

| 2.2.1       Bibliometric dataset       23         2.2.2       General IoT Publications Growth       23         2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       43         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                            |          | 2.2         | Internet of things                                    | 22       |

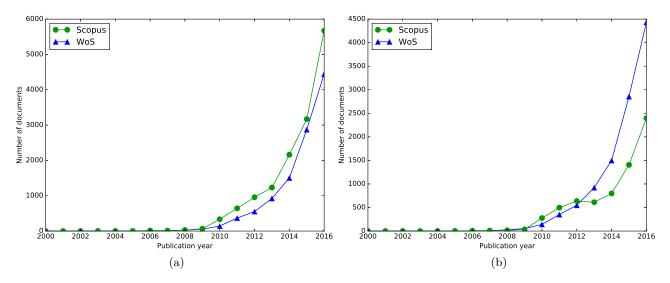

| 2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       43         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                      |          |             |                                                       | 23       |

| 2.2.3       Country and Author Research Analysis       24         2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       43         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                      |          |             | 2.2.2 General IoT Publications Growth                 | 23       |

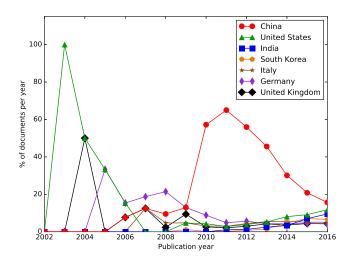

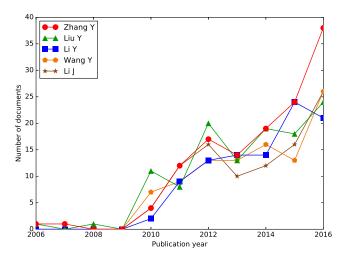

| 2.2.4       Research Topics       31         2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       43         2.3.4       Communication interfaces       44         2.3.5       Networking       46         2.3.5       Networking       50         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       65         2.4       Graphic processing units       65         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                        |          |             |                                                       | 24       |

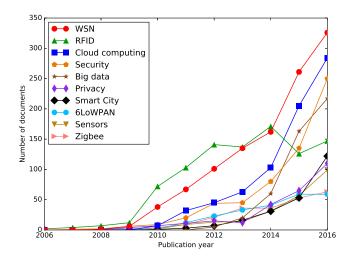

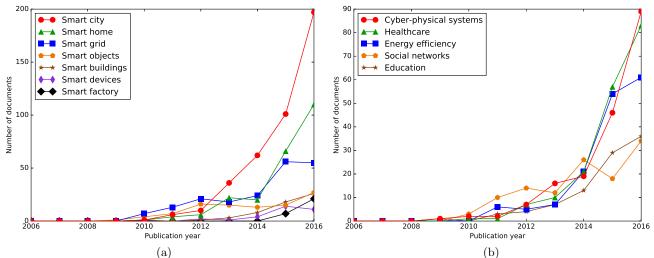

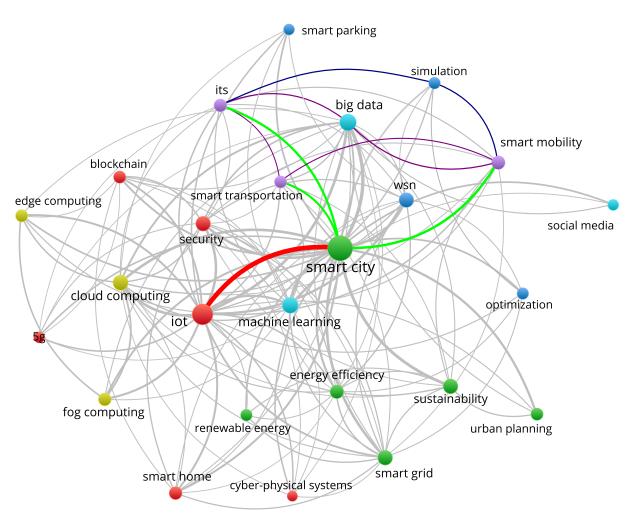

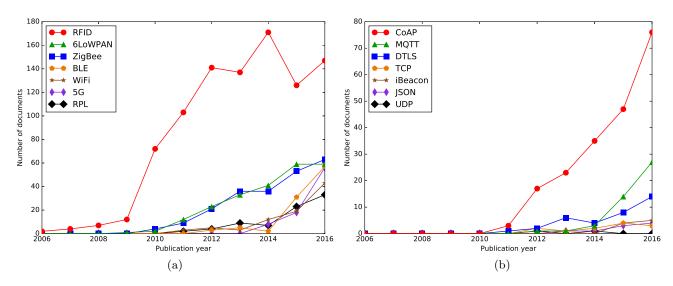

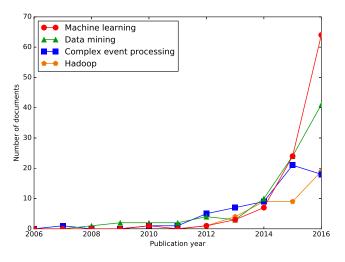

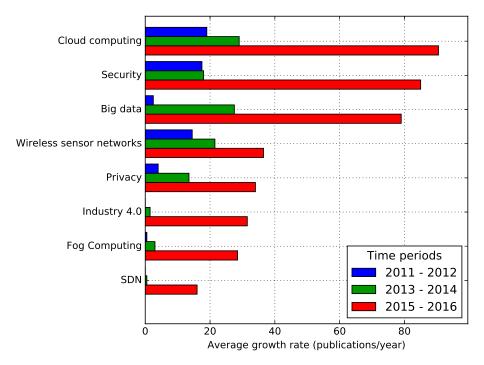

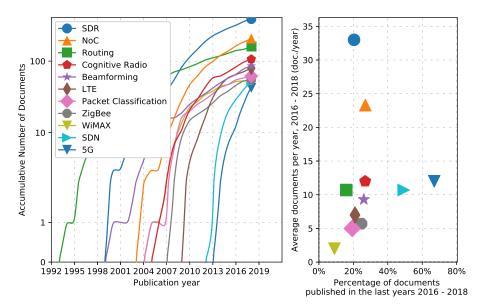

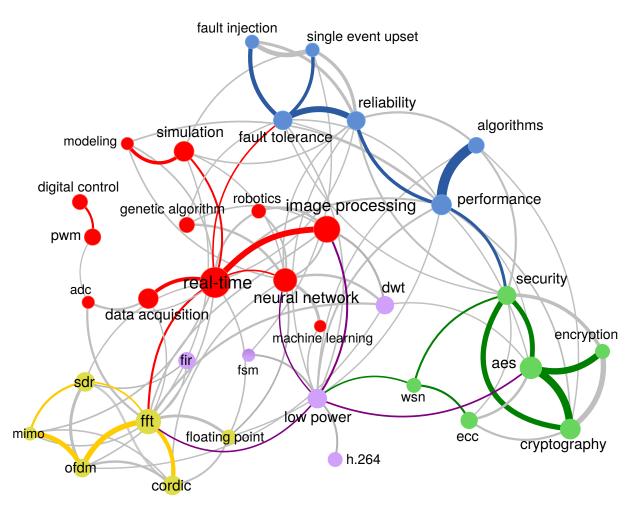

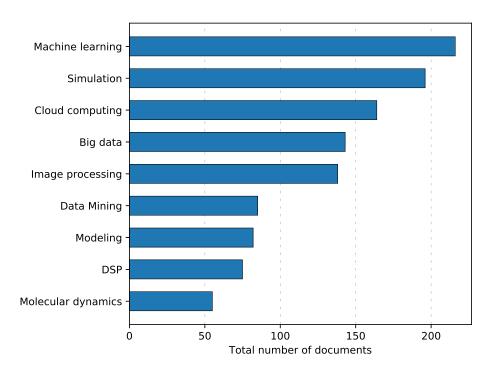

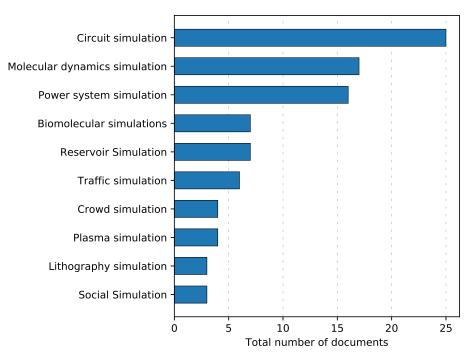

| 2.3       FPGA       41         2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       46         2.3.6       Computer security       50         2.3.7       Machine learning       50         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                          |          |             | · ·                                                   | 31       |

| 2.3.1       Dataset collection       41         2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       50         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                          |          | 2.3         |                                                       | 41       |

| 2.3.2       Review methodology       43         2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       50         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                              |          |             |                                                       | 41       |

| 2.3.3       Digital control       44         2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       50         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |             |                                                       | 43       |

| 2.3.4       Communication interfaces       46         2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |             |                                                       | 44       |

| 2.3.5       Networking       48         2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       53         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |             |                                                       |          |

| 2.3.6       Computer security       50         2.3.7       Machine learning       52         2.3.8       Digital signal processing       53         2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             |                                                       |          |

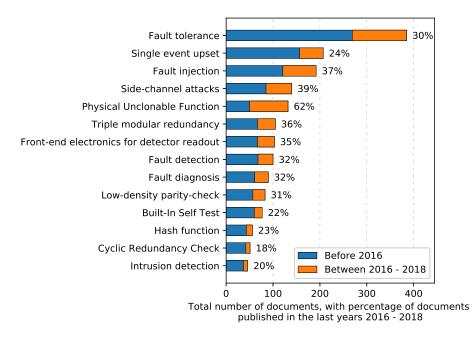

| 2.3.7Machine learning522.3.8Digital signal processing532.3.9Image and video processing562.3.10Big data582.3.11Computer algorithms592.3.12Other implementations602.3.13Other applications622.3.14Applications mapping652.4Graphic processing units682.4.1GPUs' applications68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |             |                                                       | 50       |

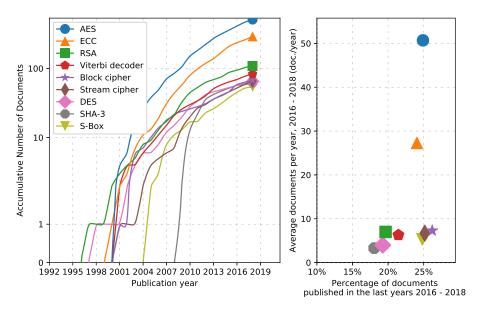

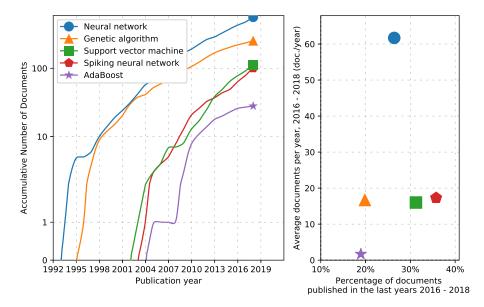

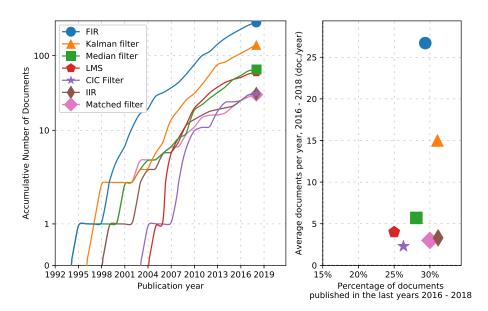

| 2.3.8Digital signal processing532.3.9Image and video processing562.3.10Big data582.3.11Computer algorithms592.3.12Other implementations602.3.13Other applications622.3.14Applications mapping652.4Graphic processing units682.4.1GPUs' applications68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             | 1 0                                                   |          |

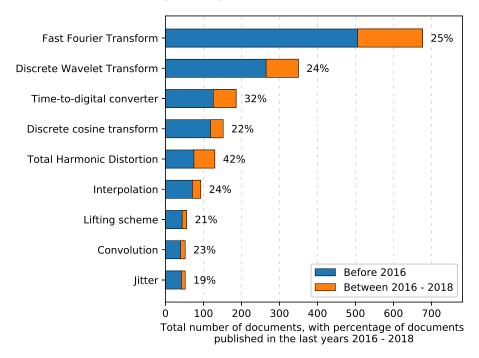

| 2.3.9       Image and video processing       56         2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |             | 0                                                     |          |

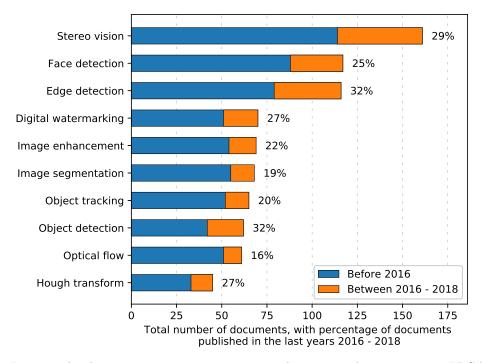

| 2.3.10       Big data       58         2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |             |                                                       |          |

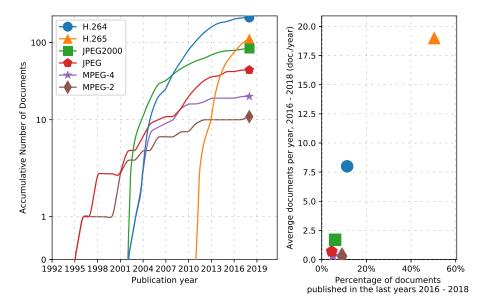

| 2.3.11       Computer algorithms       59         2.3.12       Other implementations       60         2.3.13       Other applications       62         2.3.14       Applications mapping       65         2.4       Graphic processing units       68         2.4.1       GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             | 0 1 0                                                 |          |

| 2.3.12Other implementations602.3.13Other applications622.3.14Applications mapping652.4Graphic processing units682.4.1GPUs' applications68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             |                                                       |          |

| 2.3.13 Other applications       62         2.3.14 Applications mapping       65         2.4 Graphic processing units       68         2.4.1 GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |             | 1 0                                                   |          |

| 2.3.14 Applications mapping652.4 Graphic processing units682.4.1 GPUs' applications68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             |                                                       |          |

| 2.4 Graphic processing units       68         2.4.1 GPUs' applications       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |             |                                                       |          |

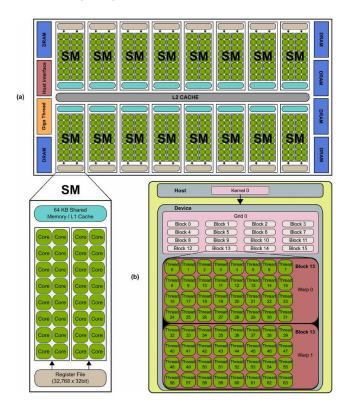

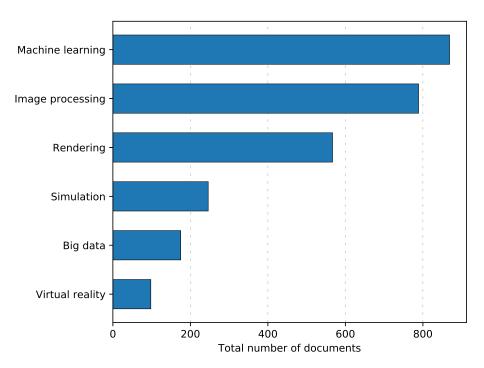

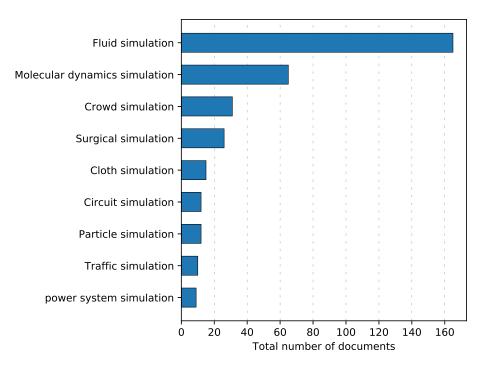

| 2.4.1 GPUs' applications $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 24          |                                                       |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | <b>2.</b> T | 1 1 0                                                 |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |             |                                                       |          |

| 2.4.3 Architecture $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             |                                                       |          |

### CONTENTS

|   | 2.5            | Multi-core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                | 2.5.1 Multi-core's applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                | 2.5.2 Multi-core-based simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 2.6            | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

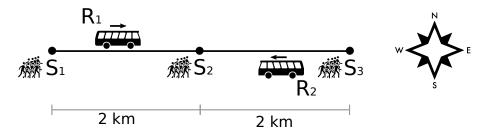

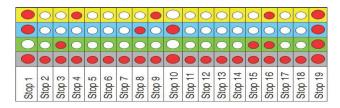

| 3 | Pub            | olic transport routes simulation 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

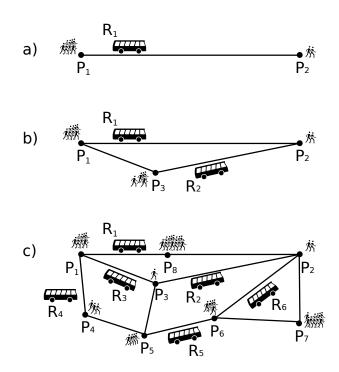

| 0 | 3.1            | Public transport system   77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 0.1            | 3.1.1 Passenger demand in public transport systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                | 3.1.2 Public transport vehicles routes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 3.2            | Simulation models and software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 0.1            | 3.2.1 Traffic simulation software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 3.3            | Traffic simulation parameters specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 3.4            | Simulation performance indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4 | <b>٦</b> .     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

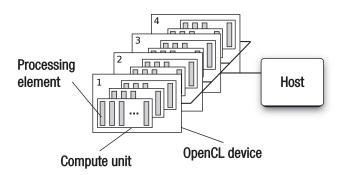

| 4 | 4.1            | sivo public transport routes simulation 85<br>OpenCL architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 4.1            | 4.1.1         Platform model         86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

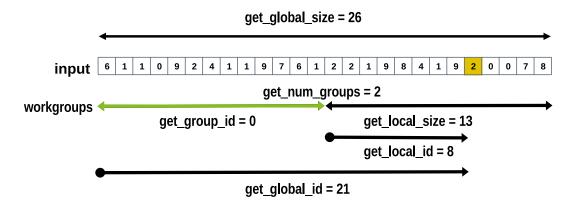

|   |                | 4.1.1         I fattorin model         80           4.1.2         Execution model         87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                | 4.1.2         Execution model         87           4.1.3         Memory model         87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                | 4.1.5         Memory models         87           4.1.4         Programming models         88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

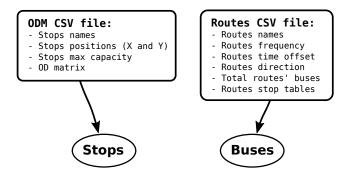

|   | 4.2            | Parameters Loading Module (PLM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 7.2            | 4.2.1 ODM CSV file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |